|

近些年来,作者走访过很多客户,结识了大量的在一线从事电源设计和开发的工程师,在和他们的交流过程中,也遇到过许多技术的问题,然后大家一些分析这些问题产生的原因,并找到相应的解决方法。在这个过程中,我遇到过困惑迷茫,也体验过成功喜悦,并和许多工程师成有为朋友,他们是我人生路的最坚实的快乐和财富,他们一直鼓励我,将遇到的许多经验分享出来,现在整理一些功率MOSFET典型的应用问题,希望对广大的电子工程师有所帮助。

问题1:在MOSFET的应用中,主要考虑的是哪些参数?在负载开关的应用中,MOSFET导通时间的计算,多少为佳?PCB的设计,铜箔面积开多大会比较好?D极、S极的铜箔面积大小是否需要一样?有公式可以计算吗?

回复:MOSFET主要参数包括:耐压BVDSS,Rdson,Crss,还有VGS(th), Ciss, Coss;同步BUCK变换器的下管,半桥和全桥电路,以及有些隔离变换器副边同步整流MOSFET中,还要考虑内部二极管反向恢复等参数,要结合具体的应用。 下面的波形为感性负载功率MOSFET开通的过程,Rg为MOSFET内部栅极电阻,Ron为MOSFET的栅极和驱动电源VCC之间的串联大电阻的和:,包括栅极外部串联的电阻以及PWM驱动器的上拉电阻。 VGS(th)和VGP在MOSFET的数据表中可以查到,有些数据表中没有标出VGP,可以通过计算得到平台的电压值。 产生开通损耗的时间段为t2和t3,t1时间段不产生开通损耗,但产生延时。 在负载开关的应用中,要保证在t3时间后,输出电容充电基本完成,就是电容的电压基本等于输入电压,在这个过程中,控制平台的电压VGP,就相当于控制了最大的浪涌电流,浪涌电流就不会对系统产生影响。因此导通时间要多长,由输出的电容和负载的大小决定。 具体的计算步骤是:设定最大的浪涌电流Ipk,最大的输出电容Co和上电过程中输出负载Io。如果是输出电压稳定后,输出才加负载,则取:Io=0。 Co×dUo/dt+Io=Ipk (4)

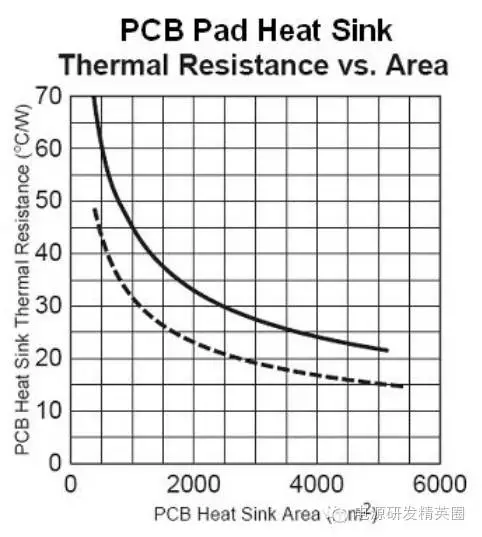

由(4)式可以算出输出电容充电时间t。负载开关的应用,通常在D和G极并联外部电容,因此,t3时间远大于t2,t2可以忽略,因此可以得到:t=t3,由(3)式可以求出D和G极并联外部电容值。 然后由上面的值,对电路进行实际的测试,以满足设计的要求。负载开关的稳态功耗并不大,但是瞬态的功耗很大,特别是长时间工作在线性区,会产生热失效问题。因此,PCB的设计,特别是贴片的MOSFET,要注意充分敷设铜皮进行散热。 在MOSFET的数据表中,热阻的测量是元件装在1平方英2OZ铜皮的电路板上。Drain的铜皮铺在整个1平方英寸、2OZ铜皮的电路板。实际应用中,Drain的铜皮不可能用1平方英、2OZ铜皮的电路板,因此,只有尽可能的用大的铜皮,来保证热性能。具体的降额值可能值可以参见以下的图。 如果是多面板,最好D和S极对应铜皮位置的每个层都敷设铜皮,用多个过孔连接,孔的尺寸约为0.3mm。

、

、

问题2:功率MOSFET的Qgs,Qgd,Ciss,Crss,Coss,tr和tf的关系?

回复: 如下图,在一定的测试条件下,Qgs与Ciss相关,Qgd与Crss相关,Qg与Crss,Ciss都相关,驱动的电压决定其最终的电荷值。Qgs和Qgd都是基于相关的电容的计算值。 tr和tf如下图,对于上升和下降的延时,和Crss,Ciss都相关。注意此时的测量条件是阻性负载。如果是感性负载,电感电流不能突变,那么由于电感的续流,这个时间就和负载的特性相关了。 上升延时tr:上升延时的定义是在MOSFET的开通过程中,VGS的电压上升,从其10%值开始,到VDS下降到为10%VDS值为止。在开通的过程中,VGS上升米勒电容平台前的时间由Ciss决定,米勒电容平台的时间Crss由决定,过了米勒电容平台到VDS下降到为10%VDS的时间又由Ciss决定。下降延时tf和tr定义类似。 问题3:AOD4126的数据表中,红色标注的ID、IDSM、IDM有什么区别?PD和PDM的值是否有标错?另外,关于RθJA和RθJC,作为用户要按照备注中的哪一项判定?对于同样规格的MOSFET,双通道和单通道相比,优势在哪里?是不是简单的Rdson减半、ID加倍等参数合成?

回复:MOSFET的数据表中,ID和IDSM都是计算值,其中,ID是基于RθJC和Rdson以及最高允许结温计算得到的,IDSM是基RθJC和Rdson以及最高允许结温计算得到的。PD和PDM也是基于上述条件的计算值。 在实际的应用中,由于MOSFET所用的散热条件不一样,因此,在开关过程中,还要考虑动态参数,所以,ID没有实际的意义。 RθJA和RθJC是二个不同的热阻值,具体的定义在数据表中有详细的说明,注意的是,数据表中的热阻值,都是在一定的条件下,测量得到的。实际应用过程中,由于条件不同,得到的测量结果并不相同。 使用双通道和单通道的MOSFET,要综合考虑开关损耗和导通损耗,Rdson不是简单的减半,因为二个功率管并联工作,不平衡性的问题永远是存在的,而且,动态的开关的过程中,容易产生动态的不平衡性。如果不考虑开关损耗,仅仅考虑导通损耗,那么还是要对Rdson作一定的降额。 问题4:不同的测试的条件为影响MOSFET的数据表中的VGS(th)和BVDSS吗?ATE是如何判断的?

回复:不同测试条件,结果会不同,因此,在数据表中,会标明详细的测试条件。对于AET的测试,以VGS(th)为例,它和Igss相关,如AON6718L,当G和S极加上最大20V电压,注意到VDS=0V,如果Igss小于100nA, 由表明通过测试。

不同的公司ST,Fairchild,IR,Vishay等,可能使用不同的Igss,如IR1010使用200nA,IR3205使用100nA。目前,行业内使用100nA更通用。同样的,BVDSS的测试条件:ID=250uA, VGS=0V,如果ID 越大,BVDSS电压值越高。 问题5:一个100V的MOSFET,VGS耐压大概只能到30V。在器件处于关断的时刻,VGD大概能到100V,是因为G和S极间的栅氧化层厚度比较厚,还是说压降主要在沉底和飘移电阻上面?

回复:GS电压主要由栅氧化层厚度控制,GD主要由EPI+层厚度来控制,所以VGD耐压高。

问题6:关于雪崩,下面描述是否正确?

1、单纯的一次击穿不会损坏MOSFET?

回复:很多时候,就是测1千片,或者1万片,电压高于额定的电压值,MOSFET也不会损坏。 2、雪崩损坏MOSFET有两种情况:一种是快速高功率脉冲,直接使寄生二极管产生较大雪崩电流,芯片快速加热过温损坏。另一种是寄生三极管导通,并发生二次击穿? 回复:是的,特别是新一代工艺的MOSFET,基本上是后一种损坏方式:寄生三极管导通。寄生三极管的导通,发生二次击穿并不全是因为雪崩发生,还可能由于dv/dt过高的原因而导致。 3、雪崩损坏都发生在VDS大于额定值的情况? 回复:是的。但是高温条件下,一些大电流的关断,可能在关断过程中,发生寄生三极管导通而损坏,虽然看不到过压的情况,但是作者仍然将其定义为:雪崩UIS损坏。 4、关于(2)中两种情况,什么情况下倾向于第一种发生,什么情况下倾向于第二种发生?

回复:如果单元非常一致,散热非常好均匀,热平衡好,第一种情况发生,早期的平面工艺有时候就会看到这种损坏模式。现在,新的工艺导致单元的密度越来越集中,产生的损坏通常用就是第二种。 作者遇到过很多的工程师问这样的一个问题:如果说UIS的雪崩损坏时,电压通常会达到耐压值的1.2~1.3倍,可以明显看到电压有箝位(通俗说法:波形砍头),那么,对于一个100V的MOSFET,工作在105V是否安全,110V是否安全?如上所述,100V的MOSFET,加上110V的电压,不会损坏,那么,安全的原则是什么呢? 对于设计工程师来说,所要求的就是在最极端的条件下,设计的参数有一定的裕量,也就是从设计的角度来说,保持系统的安全和可靠性,永远都排在最优先的位置。 因此,笔者建议的原则是:在动态的极端条件下,瞬态的电压峰值不要超过MOSFET的额定值。 问题7:关于Trench MOS的SOA, 听说MOSFET在放大区有负温度系数效应,所以容易产点。这是否就是MOSFET的二次击穿,但是,看资料MOSFET的Rdson是正温度系数效应,不会产生二次击穿。这一点,一直都没有了过,能否指点一下,后面再请教详细情况。

回复:平面工艺和Trench工艺的MOSFET都有这个特点,这是MOSFET固有特性。Rdson的正温度系数效应是在完全导通的稳态的条件,才具有这样的特性,可以实现稳态的电流均流,但是,MOSFET在动态开通的过程中,会跨越负温度系数区进入到完全开通的正温度系数区,同样,关断过程中,跨越完全开通的正温度系数区进入负温度系数区。只是因为平面工艺的单元密度非常小,产生局部过流和过热的可能性小,因此热平衡好,相对的,动态经过负温度系数区时,抗热冲击好。通常在设计过程中,要快速的通过此区域,减小热不平衡的产生。

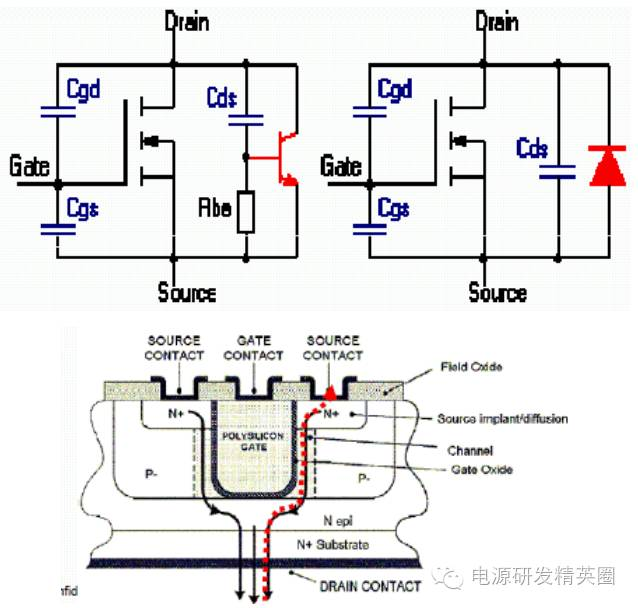

问题8:关于寄生二极管和三极管,如下理解是否正确?下图中,S极并没有和P型层直接接触,那么就不存在寄生二极管,只有寄生三极管。但是这个三极管很容易误导通,所以将P型层也直接连到S级,以消弱三极管效应。那么此时就体现为明显的寄生二极管?

回复:是的,上述的理解是正确的,目前功率MOSFET的S极都和P+连接在一起,很少用图中这样不连接的结构。主要的原因在于:对于内部寄生的三极管,S极和P+连接在一起相当于基级和发射级短路,不连接在一起相当于开路:VCES>>VCEO。这样的内部连接,也导致内部的寄生二极管功能,也连接到外部电路。

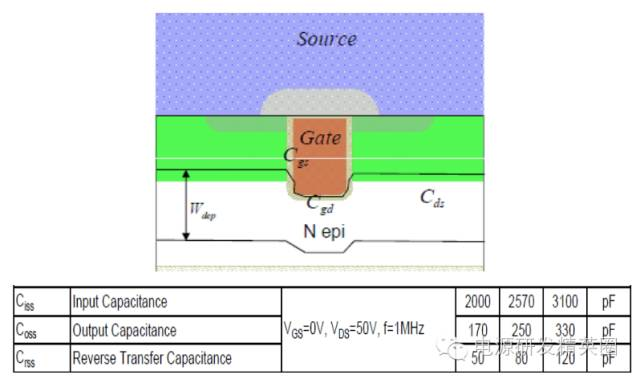

问题9:关于米勒电容Crss,在你的文档MOSFET的动态参数中,有公式如下: 参考图片,Crss电容是栅极通过氧化层对漏极的电容,对于开关过程,在第2阶段,沟道打开后,Ciss为什么增加了,是什么原因?另外,AON6450规格书上的测试条件是VDS=50V的情况,这个测试的条件基于什么原因?是否可以给出其它条件下的电容值?

回复: Ciss增加的原因是Crss增加,图中,器件导通后,Wdep减小,Crss就增加。对于一个100V的器件,比如:AON6450,由于在米勒平台区,极限的情况VGD将从100V降到10V以内。Crss是一个动态电容,容值随着VDS而变化,而且不是线性关系。 数据表中所采用的测试条件,是行业通常采用的标准,以50%的VDS测试。如果客户有特殊要求,可以提供80%或100%的数据。 问题10:功率MOSFET的SOA曲线如何得到的,可以用来作为设计的安全标准吗?

回复:任何一家公司的SOA曲线上,主要有3部分组成:电阻限制区、几条由脉冲功率限制的电流电压直线和最大电压直线。最大电压值就是数据表中的额定值。几条由脉冲功率限制的电流电压直线,实际上是计算值,就是基于数据表中的瞬态热阻、导通电阻以及最大的允许结温计算得到的,而且都是基于TC=25度,TC代表的是封装裸露铜皮的温度,在实际应用中,TC的温度远高于25度,因此,SOA曲线是不能用来作为设计的验证标准。

问题11:VGS大于VGS(th),MOSFET导通,MOSFET刚进入米勒平台,是否就算达到了饱和?如果是这样,此时停止向G极供电,假定忽略栅极氧化层的漏电,这时VDS会一直维持比较高压降吗?感觉有点不可思议,因为其饱和以后,Rdson已经降了下来。如果说没有饱和,也感觉说不过去,Rdson和VGS有关,达到10V以后,Rdson已经很小了,压降也应该降下来。如果说压降自动会降下来,那不是说米勒平台后期的充电没有什么用?

回复:VGS大于VGS(th)时,MOSFET开始导通,其刚进入米勒平台,MOSFET都工作在放大区,而且器件都没有完全导通,因为,此时MOSFET导通电阻非常大,D极的电压由整个MOSFET承受,因此电流较小,电流乘上电阻也等于VDS值,也就是D、S极所加的电源电压值。

事实上,MOSFET工作在线性区时,和线性电压调节器,也就是LDO,如LM7805的工作原理相同,如:当输入电压为10V,输出5V,压降就是5V;输入电压12V,输出还是5V,压降是7V,MOSFET相当于调节管,输入电压和输出电压的差值,都由MOSFET来承担。 到了米勒平台区,电流为系统的最大电流,电流不能再增加,那么,VDS的电压开始下降,即使是VDS的电压下降一点点,所产生的电压变化率也非常大,因此,驱动回路的电流,将全部被米勒电容Crss所抽取,此时,就看到了所谓的“米勒平台”,VDS的电压在一定的时间内,维持一个稳定的值,直到VDS完全下降到最小值,VDS的电压变化率为0时,才结束米勒平台区。 问题12:1、请教一个AOS3401的问题:现在使用AOS3401的导通电阻Rdson作为隔离电阻,用来缓冲热插入移动硬盘的瞬间冲击电流,防止瞬间把主机芯电压拉低,电路图如下,5V_USB是插移动硬盘的地方,+5V_Normal来自主机芯电压。将VGS设计在固定的-1.6V左右,此时的Rdson大约在100mΩ左右,插上移动硬盘瞬间的冲击电流由原来的9A下降到了5A左右,冲击电流持续时间80微秒左右,效果很明显,移动硬盘正常工作时电流约300mA。如果将VGS设计在-2.5V左右,Rdson只有几十mΩ,对冲击电流的抑制作用不大。这个电路的设计原则是什么? 回复:VGS=-1.6V时,可以保证MOSFET导通,注意要考虑电阻阻值的分散性,在最差的条件下,如果使用电阻的精度为10%,VGS电压绝对值:1.3+1.6*20%=1.64V,MOSFET仍然可以工作。如果电阻的精度为15%,考虑到MOSFET的VGS(th)电压的分散性,在一定的条件下,如低温,MOSFET有可能不工作。VGS(th)电压是负温度系数,温度越低,其值越大。 驱动电压的稳定值,要结合输入电压最低值,分压电阻值的精度,VGS(th)和VGS(th)的温度系数等最极端的条件下,来选择合适的分阻电阻的分压比,保证系统的设计要求。同样,PCB布板时,S和D都用大的铜皮连接,如果是多层板,在每层都放上相应大小的的铜皮,用多个10-15mil的过孔连接,散热。 2、AO3401的VGS(th)规格书中标的可以到-1.3V,设置VGS=-1.6V,电压绝对值大于-1.3V,是否该MOS正常导通,应该没有问题吧?现在损耗并不是考虑的问题,0.03V的Rdson的压降对系统没有任何影响。原来使用一个0.1欧姆的氧化膜电阻来做隔离的,但是该电阻体积太大,用这个电路的目的就是想替换这个电阻。由于这个电路中,MOSFET是在电视机开机后一直导通的,在MOSFET一直导通的状态下,来插入移动硬盘的,而不是插入移动硬盘后再打开MOS的,所以觉得调节R45/R46/C18的值不能起到降低冲击电流的作用。希望利用MOSFET的恒流区特性来降低冲击电流,如果把VGS调整到-2.5V以上,对冲击电流的限制作用就非常小了,只能从9A降到8A左右,这样的做法对MOS来说会有问题吗? 回复:事实上,下面的电路是利于MOSFET在开通过程中,较长时间工作在线性区(放大区,也就是恒流区),从而控制上电时瞬态大负载,如热插拨移动硬盘,因为硬盘带有较大的容性负载,切入瞬间形成较大的浪涌电流.如果MOSFET已经导通,后面再插入移动硬盘这样的大容性负载,浪涌电流主要由输出端的大电容来提供,因此MOSFET无法限制浪涌电流。

MOSFET工作在线性区时,电阻远大于完全导通的电阻,因此也可以理解为用电阻抑止浪涌电流。通常,这种负载开关电路,设计时,分压电阻是为了防止VGS的最大电压超过额定的最高电压,串联在G极的电阻调节MOSFET的开通速度。在保证要求的开通速度条件下,VGS不能超过最大额定电压时,可以适当提高电阻值,这样,在正常的工作状态下,MOSFET完全导通后,减小产生的静态损耗。 3、在AO3401规格书的第1页有写operation with gate votages as low as 2.5V,是否是要求G极电压必须大于2.5V? VGS必须小于-2.5V?设计VGS=-1.6V有没有问题?如果继续加大VGS到-1V呢?是不是VGS的大小没有关系,只要保证Rdson产生的功耗不要导致MOSFET过热就行,是否正确?

回复:不能那么认为,这句话的含义是:AO3401可以工作在VGS=-2.5V,此时,导通电阻约为120mOhm。如果VGS电压太小,低于阈值电压VGS(th),AO3401可能无法完全开通,无法正常工作。还是建议将VGS设计在-2.5V以上,如-3.5V左右,通过调节(增加)R45/46和C18来降低冲击电流。

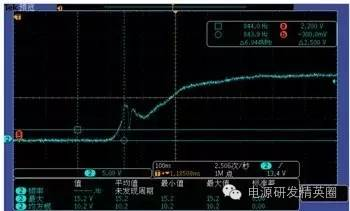

问题13:使用如下电路,用CPU的GPIO口直接控制一个MOSFET管,MOSFET作为后端负载的开关,这种应用有什么风险? 回复:检查VCC以及MR34/MR35分压后的电压值VGS,VGS绝对值要比MQ1的VTH高,才能保证MOSFET完全打开,否则后面的系统可能不工作;同时,检查GPIO口的驱动能力,是否满足驱动的要求。如果很小,最好用GPIO口驱动一个三极管的B极,三极管的集电极C下拉MOSFET的G极。 由实际的浪涌电流,再调整MC11值,以及MR34/MR35值。在PCB设计时,MQ1的D,S用大铜皮连接,如果多层板,在多个层放铜皮,用多个过孔,分别进行连接。 问题14:想请教一个有关MOSFET的关断时DS电压振荡的问题,在同一个电路上测试了两个不同厂商的30V的MOSFET,得到了关断时不同的DS电压波形,如下图。可以看到器件1的尖峰较高,但是振荡抑制的很快;器件2的尖峰较低,但是振荡抑制的较慢。因为是在同一块PCB上测量的,所以电路的寄生电感,电阻等参数是不变的,现在只有器件不同。这种尖峰是电路上的寄生电感和MOSFET的电容谐振引起,但是不明白具体是这两个器件哪个参数的差别,会使得这种振荡表现这么不同。是否能够从器件数据的某些参数对比来选择一款实际应用峰值较低,振荡又能快速消除的MOSFET呢? 回复:这样的振荡波形,对于一个电源的工程师来说,经常看到,在这里,首先谈一下测量方法的问题: (1)如同测量输出电压的纹波一样,所有工程师都知道,要去除示波器探头的帽子,直接将探头的信号尖端和地线接触被测量位置的两端,减小地线的环路,从而减小空间耦合的干扰信号。 (2)带宽的问题,测量输出电压纹波的时候,通常用20MHZ的带宽,但是,测量MOSFET的VDS电压时候,用多少带宽才是正确的测量方法?事实上,如果用不同的带宽,测量到的尖峰电压的幅值是不同的。 具体原则是:①确定被测量信号的最快上升Tr和下降时间Tf;②计算最高的信号频率:f=0.5/Tr,Tr取测量信号的10%~90%;f=0.4/Tr,Tr取测量信号的20%~80%;③确定所需的测量精确度,然后计算所需的带宽。 在上图波形中,被测量信号最快的下降时间为2ns(10%~90%),判断一个高斯响应示波器在测量被测数字信号时所需的最小带宽:f=0.5/2ns=250MHz。 若要求3%的测量误差:所需示波器带宽=1.9*250MHz=475 MHz;若要求20%的测量误差:所需示波器带宽=1.0*250MHz =250MHz。因此,决定示波器带宽的重要因素是:被测信号的最快上升时间。注意:示波器的系统带宽由示波器带宽和探头带宽共同决定。 VDS的振荡波形由PCB寄生回路电感和MOSFET的寄生电容形成高频谐振而产生的,在寄生电感值一定的条件下,寄生电容越小,振荡的频率越高,幅值也越高,同时,振荡的幅值和回路的初始电流值相关。特别注意的是:寄生电容Coss不是线性的,随着电压的增大而减小,因此,可以的看到波形振荡的频率并不是固定的。 VDS的高频振荡是无法消除的,增加Coss或在D、S极外部并联电容,可以降低振荡的频率和幅值,Snubber电路也是利用这个原理,抑制电压的尖峰。 问题15:功率MOSFET的耐压为什么是正温度系数?温度高,功率MOSFET的耐压高,那是不是表明MOSFET对电压尖峰有更大的裕量,MOSFET更安全?

回复:随着温度的升高,晶格的热振动加剧,致使载流子运动的平均自由路程缩短。因此,在与原子碰撞前由外加电场加速获得的能量减小,发生碰撞电离的可能性也相应减小。在这种情况下,只有提高反向电压,进一步增强电场,才能发生雪崩击穿,因此雪崩击穿电压随温度升高而提高,具有正的温度系数。

MOSFET耐压的测量基于一定的漏极电流,温度升高时,为了达到同样的测量漏极电流,只有提高电压,表面上看起来,测量的耐压提高了。但是,MOSFET损坏的最终原因是温度,更多时候是局部的过温,导致局部的过热损坏,在整体温度提高的条件下,MOSFET更容易发生单元的热和电流不平衡,从而导致损坏。 问题16:使用下图的电路,进行不同电平信号间的转换,VCC_SIM=5V,SIM_DATA、SIM_CARD_I/O属于I/O双向传输。SIM_DATA为输入信号,可以理解:SIM_DATA为高时,Q7截止,SIM_CARD_I/O接收为5V信号;SIM_DATA为低时,Q7导通,SIM_CARD_I/O接收为低电平信号。当SIM_DATA为输出信号时,如何理解SIM_CARD_I/O输入为低电平信号? 回复:功率MOSFET的电流可以从D到S,也可从S到D,只是从S到D是不可控的,此时,体内寄生的二极管导通。当功率MOSFET作同步整流管时候,通常也是寄生二极管先导通,然后栅极信号驱动MOSFET的导通:沟道导通,用以减小导通损耗。 SIM_DATA为输出信号时,SIM_CARD_I/O为低电平,Q7体内寄生二极管导通,信号SIM_DATA也拉低,接收低电平信号。SIM_CARD_I/O输出高电平5V时,Q7体内寄生二极管截止,信号SIM_DATA上拉到3.3V,接收高电平信号。 问题17:功率MOSFET的数据表中dv/dt为什么有二种不同的额定值?如何理解体二极管反向恢复特的dv/dt?

回复:在反激电源中,原边主开关管关断过程中,VDS的波形从0开始增大,因此产生一定的斜率dv/dt,同时产生电压尖峰,就是寄生回路的电感和MOSFET的寄生电容振荡形成的。这个dv/dt会通常通过米勒电容,耦合到栅极,在栅极上产生电压,如果栅极电压大于阈都电压,MOSFET会误导通,产生损坏,因此,要限制MOSFET关断过程中的dv/dt,

另一种情况,就是在LLC,半桥和全桥电路,以及同步BUCK的下管,当下管关断后,下管的寄生二极管先导通续流,然后对应的上桥臂的上管开通,二极管在反向恢复过程中,也会产生dv/dt的问题。通常,二极管反向恢复的dv/dt额定值,远小于MOSFET本身的dv/dt额定值。 通常,在二极管在反向恢复过程中,如果存储的电荷没有完全清除,二极管也就是下管,是不能承受 压降的,下管相当于短路,那么,在上管开通的过程,电源的电压就只能加在回路的杂散电感上:下管短路,输入电流要急剧增加,回路的杂散电感将限制电流增加,因此,电源的电压就只能加在回路的杂散电感上,这个过程持续时间越长,短路电流冲击越大,MOSFET就可能在二极管的反向恢复过程中,发生损坏。至于损坏的是上管还是下管,取决于那个功率的抗冲击能力强。

问题18:AOD2922_10用于BOOST电路,LED背光驱动器,发现其中有一颗MOSFET失效,G、D、S短路,继续工作一些时间后,D、S又变成开路,为什么?

回复:开始的失效发生在硅片内部,应该是内部D、G击穿,从而导G、D、S短路,继续工作一些时间后,由于大电流的冲击,导致S和硅片的连线熔化烧断开,因此,D、S开路。

问题19:在应用中会存在米勒平台掉沟的现象,这个掉到开启电压以下是否存在风险?

回复:如果是反激的DCM,没有影响,如果是反激的CCM,系统容易不稳定,影响MOSFET的安全性。如果是PFC的多管并联工作,那么,MOSFET在开通过程不能很好的均流,损坏的风险很大。

问题20:在一些应用中常用几个MOSFET并联扩流或散热,当用有保护的电源调试系统时不小心电路出了问题时通常只会烧一个管,如何判断是那个MOSFET损坏?

回复:用万用表打在电阻挡,检测每个MOSFET的D-G的电压,红笔接D,电阻最小的那个MOSFET就是损坏的那个。

问题21:480W的隔离电源模块中,是原边全桥整流管。模块输入电压51V~56V DC,额定输出10.8V,48A。这次坏掉的是一个桥臂上的两颗管子。在应用时因为外围电路异常造成二次侧电流反灌到原边整流管,电流从Source流向Drain的状态。结合FA报告中的Source面上的烧毁痕迹,原因分析是电流的EOS,能否证明是因为电流从S往D流动造成source烧掉?

回复:对于同步整流,输出的反灌电流是最恶劣的一种条件,在设计的过程中要尽可能的减小输出的反灌。

(1) 输出反灌形成输出整流管的雪崩,导到输出同步的整流管损坏,当然,取决于输出同步的整流管的雪崩能力,以及反灌电流形成的负向电流的大小。(2) 输出反灌电流会影响原边MOSFET工作。当输出形成反向电流的时候,若Q1/Q2是一个半桥臂,Q1为上管,Q2为下管;Q3/Q4是另外一个半桥臂,Q3为上管,Q4为下管;若不是全桥移相软开关,而是平常的PWM工作,由于是输出是反向电流,因此当Q1/4导通前,电流从Q1/4二极管中流过,而且Q1/4导通后,会从Q1/4沟道流过,当副边输出电感的能量足够大时,其原边电流不足以反向,因此Q1/4关断后,电流还得从Q1/4二极管中流过,经过死区时间后,Q2/Q3导通,此时,由于Q1/4二极管中流过电流时间长,电流也比较大,而且死区时间短,对于一些MOSFET的二极管,反向恢复的时间不是够的,就是Q1/4体二极管电荷没有完全恢复的话,这时,Q2/3导通,会导致上管桥直通,导到损坏。 至于损坏的是上桥还是下桥,那就看那个管子存受短路的能力更强。同样,是损坏原边还是副边,也看那边管子的能力更强。 -- 对于副边,是大电流关断后的电压雪崩。 -- 对于原边,是二极管反向恢复上下桥直通形成大电流损坏。 通常,二极管也是负温度系数,其导致损坏和开通时过线性区热量的积累导致的损坏形态比较接近,对应着二极管没有完全恢复的MOSFET形态。因些,对于这个例子,最好的办法,从设计角度来说,还是减小输出反灌电流。从器件来说,提高原边MOSFET的体二极管的反向恢复特性,可以提高原边器件的安全性,当然,最终的方法还是控制输出反灌电流,才能真正保持系统安全性。

问题22:MOSFET的电压测量时候电流是250uA,而IDSS电流只有几个uA,为什么?

回复:IDSS电流小,表明实际的漏电流小于测试规范的要求,因此是合格的。

问题23:MOSFET损坏后,阻抗变为一个中间值,有时工作有时不工作,为什么?

回复:通常MOSFET损坏后,如果电源没有电流保护,经过更大的电流冲击,导致内部的金属线熔化汽化,系统不工作后,MOSFET冷却下来,熔化汽化的金属凝固,局部的区域连通,形成较大的阻抗。MOSFET通电工作后,这些局部的连通区域又断开,MOSFET停止工作。有时也会出现这样的现象:冷却凝固后内部的金属断开,通电后金属熔化又导致内部区域连通。

问题24:测试MOSFET体内二极管的反向恢复时,IF越低,Qrr越大,电压尖峰越高,为什么?

回复:在MOSFET的体二极管导通时,电荷在P/N结积累,当二极管开始承受阻断电压时,这些电荷将被清除。如果IF低, P/N结积累的电荷水平低,清除的速度快,dv/dt就大,Cdv/dt的偏移电流就大。测试的Qrr包括和真正的Qrr以及Cdv/dt相关的少子,因此,测试的Qrr在低IF越大。

|