摘要近年 LCC 谐振变换器备受关注,因为它优于常规串联谐振变换器和并联谐振变换器:在负载和输入变化较大时,频率变化仍很小,且全负载范围内切换可实现零电压转换(ZVS)。本文介绍了LLC 型谐振变换器的分析方法,回顾了LLC 型谐振变换器的实际设计要素。其中包括设计变压器和选择元器件。采用一设计实例,逐步说明设计流程,有助于工程师更加轻松地设计LLC 谐振器。

引言

功率变换器设计中,对增大功率密度,缩小设计尺寸的要求越来越高,迫切需要设计师提高开关频率。采用高频工作将大大降低无源器件的尺寸,如变压器和滤波器。但存在的开关损耗却对高频工作带来不利影响。为减少开关损耗,使高频工作正常,故提出谐振切换技术 。这些技术按正弦波处理功率,并且开关器件可以很方便地软换向。因此,开关损耗和噪声可大幅度减少。常规谐振器使用串联的电感电容作为谐振网络。负载连接有两种基本结构,串联和并联。

对于串联谐振变换器(SRC), 整流负载网络与一个LC 谐振网络串联,如图1 所示。从这个结构看来,谐振网络与负载作为一个分压器。通过改变驱动电压Vd的频率,改变谐振网络的阻抗。输入电压将分配到这部分阻抗和反射负载上。因为,它是一个分压器,SRC 直流增益始终小于1。在小负载条件下,负载阻抗相对于与谐振网络的阻抗非常大;全部输入电压落在负载上。这使得人们很难在小负载条件下调节输出。理论上,在没有负载的情况下调节输出,频率会变为无限大。

对于并联谐振变换器,整流负载网络与谐振电容是并联的,如图所示。由于负载同谐振网络是并联的,因此不可避免地存在着大量的循环电流。这使得人们难以在大功率场合下使用并联谐振电路。

为了解决传统谐振变换器的局限性,提出了LLC 谐振变换器。对比常规谐振器,LLC 型谐振变换器具有许多优点。首先,它可以在输入和负载大范围变化的情况下调节输出,同时开关频率变化相对很小。第二,它可以在整个运行范围内,实现零电压切换(ZVS)。最后,所有寄生元件,包括所有半导体器件的结电容和变压器的漏磁电感和激磁电感,都是用来实现ZVS 的。

本文讲述了一种半桥LLC 谐振器的分析和设计要素。利用基波近似法分析了电压和电流波形,并得到了系统增益方程。选择一个输出为120W/24V 直流/直流转换器的设计作为典型的例子,来说明设计流程。

工作原理和基波近似

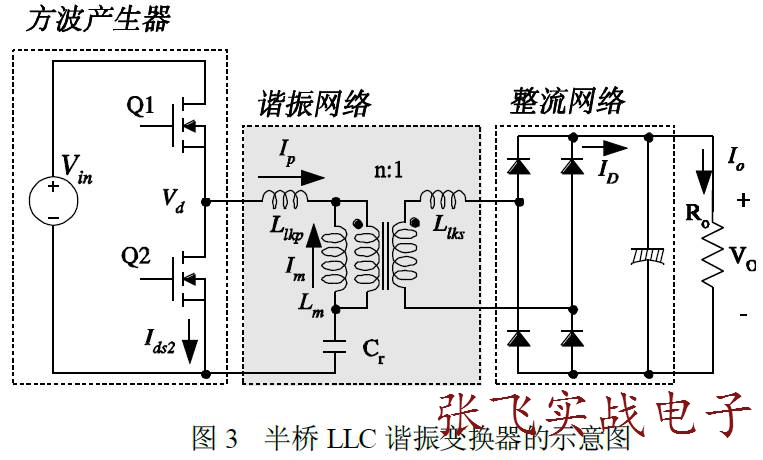

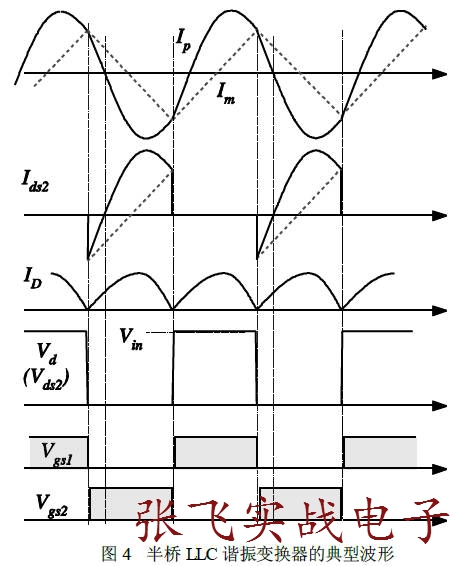

图3 为半桥LLC 谐振变换器简化示意图,图4 是它的典型波形。图3 中,Lm 是变压器励磁电感,Llkp 和Llks 分别表示变压器初级和次级的漏感。LLC 谐振变换器的工作原理和传统LC 串联谐振变换器是类似的。唯一不同的是,激磁电感相对较小,因此Lm+Llkp 和Cr 之间的谐振会影响变换器的工作。由于激磁电感较小,存在着相当大的磁化电流(Im),如图4 示。

一般来说,LLC 谐振拓扑包括三部分,如图3 所示;方波发生器,谐振网络和整流网络。

- 方波发生器,通过每次切换都以50%占空比交替驱动开关Q1 和Q2 产生方波电压Vd。方波发生器级可设计成一个全桥或半桥型。

- 谐振网络包括一个电容器,变压器的漏磁电感和激磁电感。谐振网络可以滤掉高次谐波电流。因此,即使方波电压应用于谐振网络,基本上只有正弦电流允许流经谐振网络。电流(Ip)滞后于施加于谐振网络的电压(也就是说,方波电压(Vd)的基波施加到了半桥上的图腾),这允许零电压开启MOSFET。从图4可以看到,当电流流经反向并联二极管时,MOSFET开启电压为零。

- 整流网络通过整流二极管和电容器调整交流电,输出直流电压。整流网络可设计成一个带有电容输出滤波器的全桥或中心抽头结构。

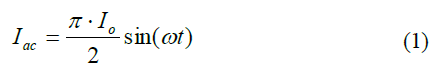

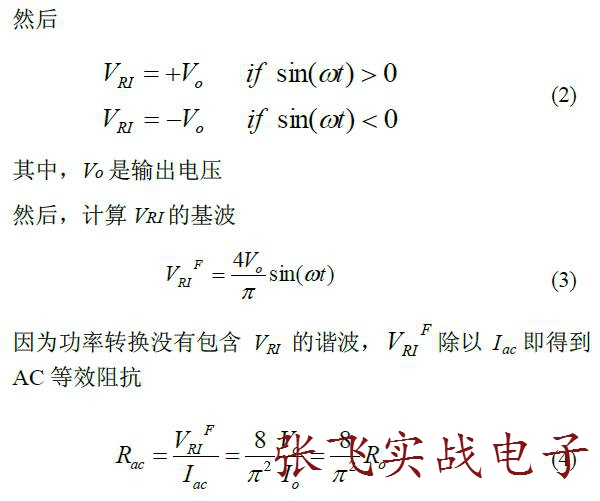

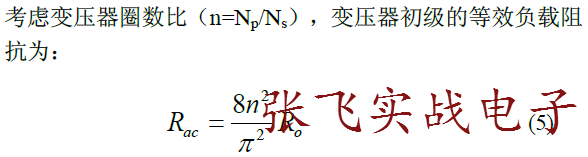

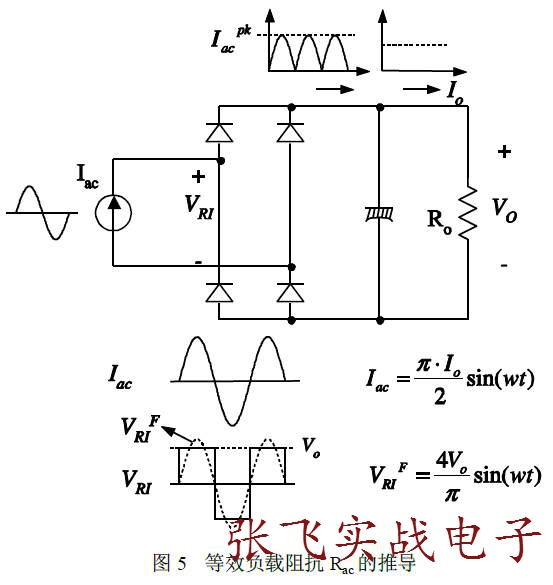

谐振网络的滤波功能可以让我们用经典的基波近似原理获得谐振器的电压增益,假定只有输入到谐振网络的方波电压的基波有助于功率传递到输出。由于次级整流电路起到一个阻抗变压器的作用,等效负载电阻与实际负载电阻是不同的。图5 显示了如何得到等效负载电阻。初级电路被替换成一个正弦电流源Iac和方波电压VRI,作为整流器输入电压。因为Iac的平均值是输出电流Io,可得到:

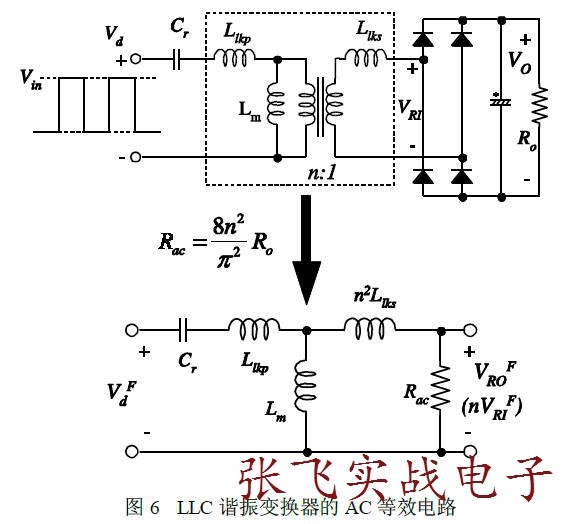

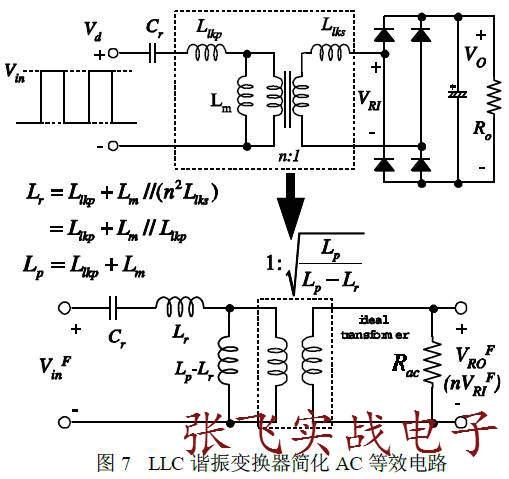

利用等效负载阻抗,得到AC 等效电路,如图6 所示,VdF和VROF分别表示驱动电压Vd 和反射输出电压VRO(nVRI)的基波。

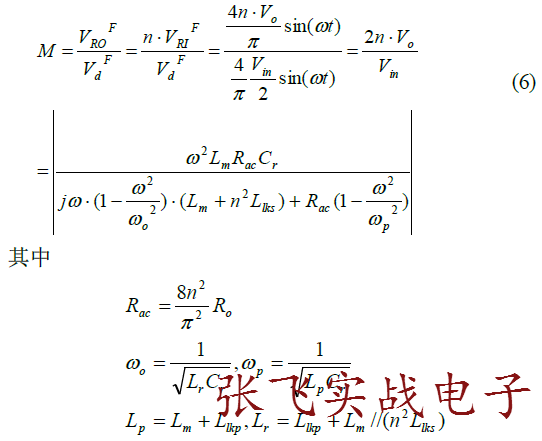

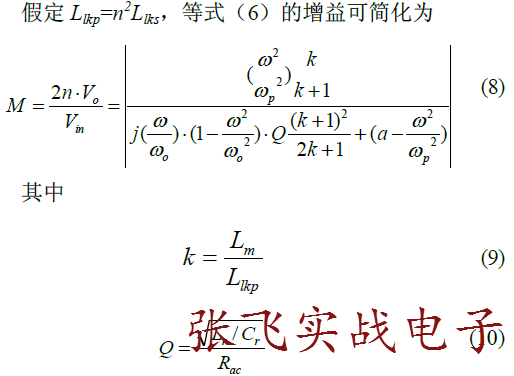

利用等式 (5) 的等效负载阻抗,得到LLC 谐振变换器特性。利用图6 示AC 等效电路,计算电压增益M

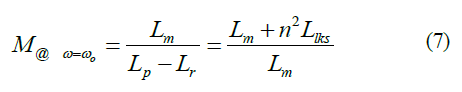

从等式(6)可以看出,电路有两个谐振频率。一个由Lr 和Cr确定,另一个由Lp 和Cr 决定。在实际变压器中,分别利用次级线圈开路和短路在初级测得Lp 和Lr。

等式(6)需要关注的是,在谐振频率(ωo)处,不管负载怎么变化增益都是固定的。

不考虑变压器次级的漏磁电感,等式(7)的增益变成1。在以前的研究中,变压器次级的漏磁电感常被忽略,以简化增益方程。然而,可以看到,如果忽略变压器次级漏磁电感,计算的增益会存在相当大的误差,导致设计结果不正确。

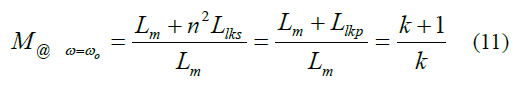

等式(7)中谐振频率(ωo)下的增益也可以简化成用K 表示的等式

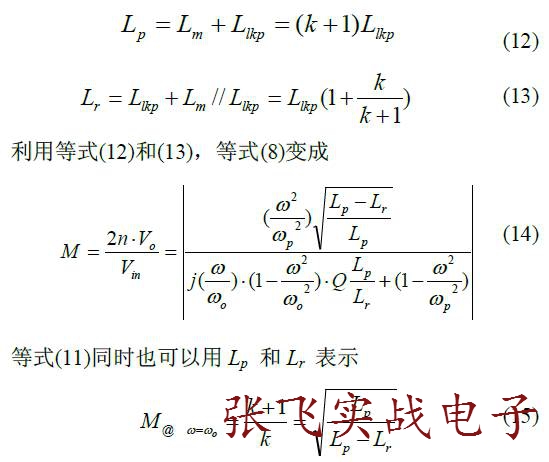

尽管增益表示成等式(8),当操作一个实际的变压器时,增益最好表示成Lp 和Lr 的函数。因为这两个量是很容易测量的。把Lp 和Lr 用K 表示,我们可以得到:

利用等式(15)计算的谐振频率增益作为变压器的一个虚拟增益,图6 所示的LLC 谐振器的AC 等效电路可以简化只含有Lp 和Lr 的形式,如图7 示

图(8)给出了不同Q 值下等式(8)的增益,其中k=5,fo=100kHz 和fp = 55kHz。从图8 可以看出,当开关频率约等于谐振频率fo 时,LLC 谐振器的特性几乎与负荷无关。这是LLC 型谐振变换器一个独特的优势,与常规串联谐振变换器相比。因此,最好让变换器工作在谐振频率周围,以减少小负载情况下开关频率的变化。

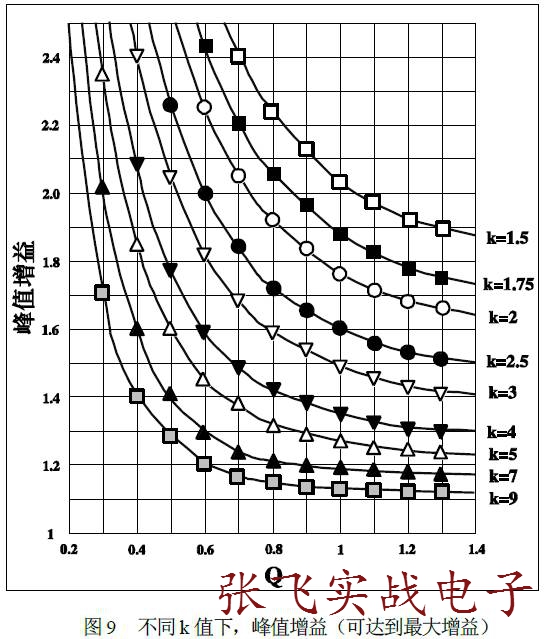

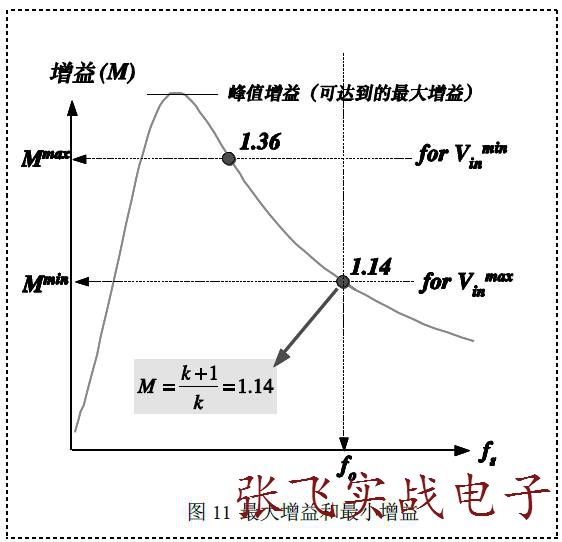

LLC 谐振变换器的工作范围受到峰值增益(可达到的最大增益)的限制,即图8 中‘*’表示的位置。需要注意到,峰值电压增益不发生在fo 也不是fp。峰值增益对应的峰值增益频率在fp 和fo 之间,如图8 示。随Q 值降低(负载减少),峰值增益频率向fp 移动,并且峰值增益较高。随Q值上升(负载增加),峰值增益频率偏向fo,峰值增益下降。因此,满负载状态应该是谐振网络设计要考虑的最坏情况。

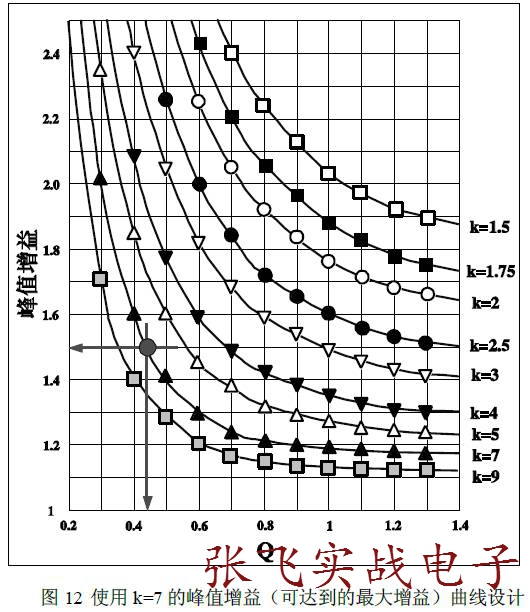

另一个决定峰值增益的重要因素是Lm 和Llkp 之间的比值,即等式(9)中定义的K 值。即使通过等式(8)能够获得某一特定条件下的峰值增益,但是要用很简洁的形式表达峰值增益是很困难的。此外,对于谐振频率(fo)以下的频率,从等式(8)求得的增益,因为基本近似,存在一定的频率误差。为了简化分析和设计,通过使用模拟工具可以获得峰值增益。图9 说明了对于不同的k 值,峰值增益(可达到最大增益)是怎样随Q 变化的。由此看来,降低K 或Q 值能够获得较高的峰值增益。对于给定的谐振频率(fo)和Q 值,降低K 意味着减少激磁电感,导致循环电流增加。因此,需要在可用增益范围和传导损失之间作一个折中。

设计流程

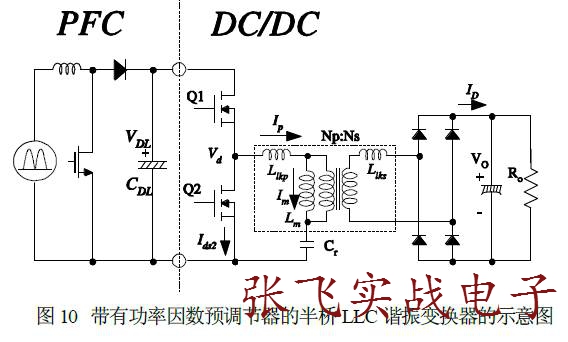

在本节中,使用图10 的示意图作为参考,来讲述设计流程。选择一个输出125W/24V 的直流/直流变换器作为设计实例。设计规格如下:

- 输入电压:380Vdc(PFC 级输出)

- 输出:24V/5A(120W)

- 保持时间要求:17ms

- PFC 输出端的直流环节电容:100uf

[第一步] 定义系统参数

第一步必须定义以下参数。

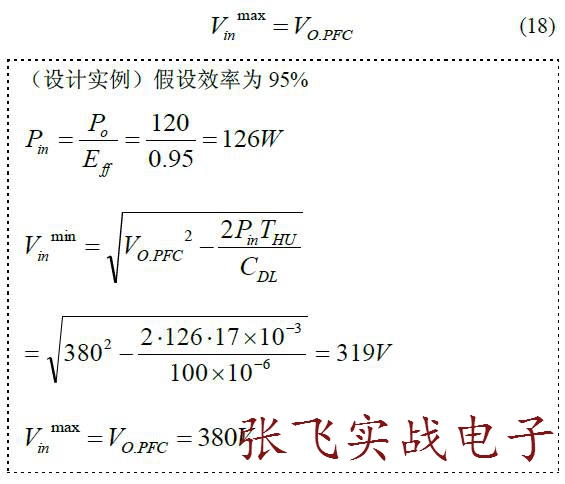

预估效率(Eff):估计电源转换效率主要用来计算某一最大输出功率下的最大输入功率。如果没有可用的参考值,对于低压输出应用场合,Eff 一般取0.88~0.92;对于高压输出应用场合,Eff 一般取0.92~0.96。有了预估效率,可以计算最高输入功率

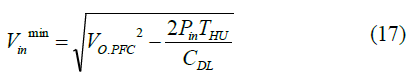

- 输入电压范围(Vinmin和Vinmax):通常情况下,假定输入电压由功率因数校正(PFC)预调节器输出提供。当PFC输出提供输入电压,考虑到保持时间的要求,最小输入电压为

其中VO.PFC 是PFC 额定输出电压,THU是保持时间,CDL是直流环节(DC link)大电容。

最大输入电压是:

[第二步] 确定谐振网络的最大和最小电压增益

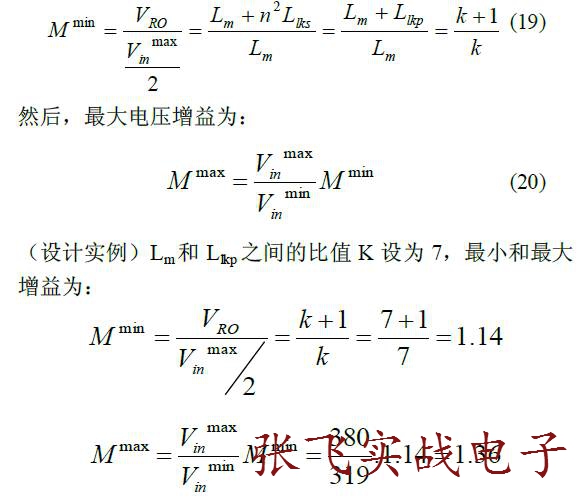

在上一节讨论中,为了最大限度地降低开关频率变化,LLC谐振变换器一般运行在谐振频率(fo)附近。当输入电压由PFC 输入提供时,输入电压在正常运行时拥有最大值(PFC额定输出电压)。把变换器最大输入电压情况下的工作频率设计为谐振频率(fo),最小增益应该发生在谐振频率(fo)。从等式(11)看出,fo 增益是激磁电感和初级漏磁电感之间比值(k=Lm/Llkp)的函数。因此,必须选择合适的k 值以获得最小增益。然而,一个小的k 值仍可获得较高的峰值增益,太小的k 值会使得变压器耦合性差,效率低。一般,k 取5~10,此时谐振频率(fo)下的增益为1.1~1.2。当确定k 值后,就可以确定最大输入电压(Vinmin)情况下的最小电压增益

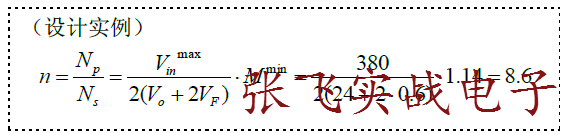

[第三步] 确定变压器圈数比 (n=Np/Ns)

因为整流网络使用全波桥式整流器,变压器圈数比为:

其中,VF 是次级整流二极管的压降。

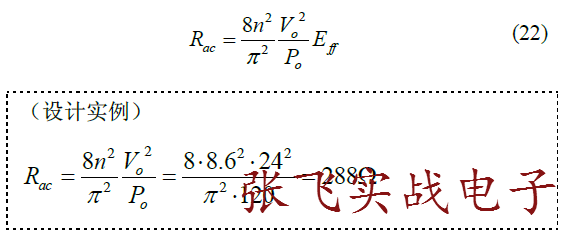

[第四步] 计算等效负载阻抗(Rac)

用等式21 求得变压器的圈数比,计算等效负载阻抗

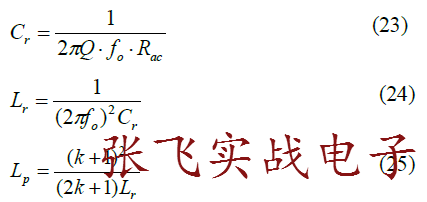

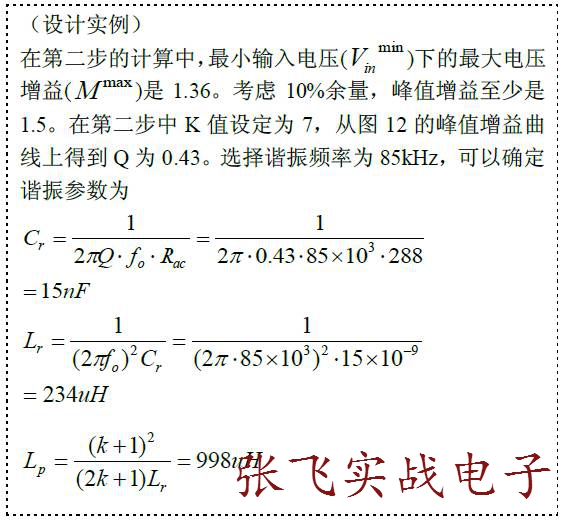

[第五步] 设计谐振网络

利用第二步选择的K 值,从图9 的峰值增益曲线中读取合适的Q 值,以确保足够的峰值增益。一般,在峰值增益上要有10~15%余量。然后,可以计算谐振参数

[第六步] 设计变压器

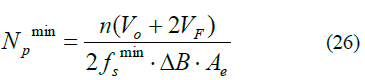

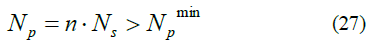

变压器设计的最坏情况是最低开关频率条件,发生在最低输入电压和满负载情况下。为了计算最低开关频率,利用等式(8)画出增益曲线,读取最小开关频率。然后,利用下面的等式计算变压器的初级最小线圈数

其中,Ae 是变压器磁芯的横截面积,单位m2 ,△B 是磁通密度的最大摆幅,单位特。如果没有参考数据,△B 可以取0.25~0.3T

然后,选择次级线圈数,保证初级线圈数大于Npmin

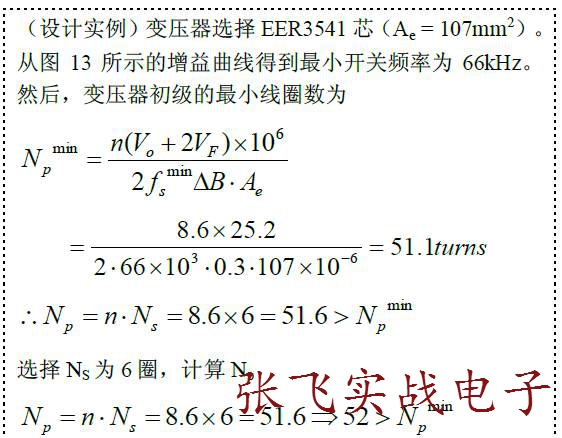

[第7步] 变压器构造

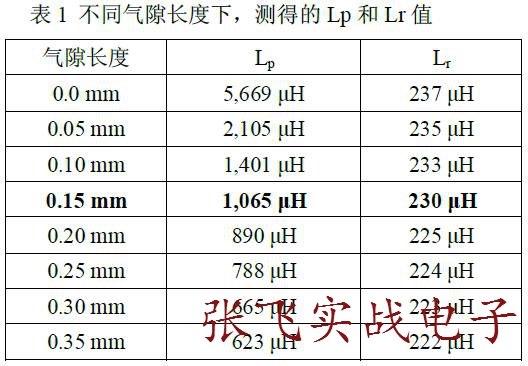

在第五步中,确定了变压器的参数Lp和Lr。Lp和Lr 是可以分别利用次级线圈开路和短路,在初级测量的。由于LLC变换器设计需要一个相对大的Lr,一般采用一种可组合线轴,如图14 所示,以获得理想的Lr值。对于这种可组合线轴,线圈数和绕线结构是决定Lr 大小的主要因素,而变压器芯的气隙长度不会影响Lr太多。但是,通过调整气隙长度却可以轻松控制Lp。表1 显示了不同气隙长度下测得的Lp和Lr 值。假设气隙长度为0.15mm,可以获得Lp和Lr值。

即使在LLC 谐振变换器设计中,这种整合变压器的办法,能够将磁性元件集中到一个单独的芯中,从而节省了一个磁性元件,但是Lr 在实际变压器设计中是不容易控制的。因此,设计谐振网络有时需要利用变压器制造后实际测得的Lr 值。或者增加一个谐振电感,和谐振电容串联,获得理想的Lr 值。

[第八步] 选择谐振电容

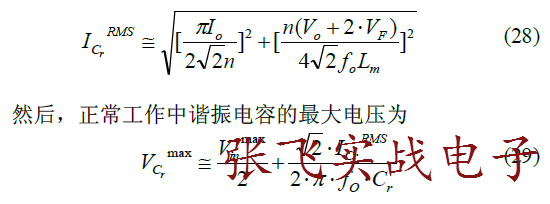

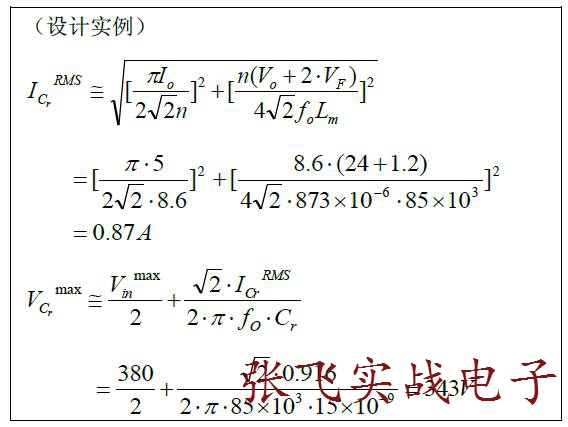

选择谐振电容时,必须考虑额定电流,因为会有相当数量的电流流经电容。通过谐振电容器均方根电流为

结论

本文讲述了一种利用变压器的激磁电感和漏磁电感作为谐振元件的LLC 谐振变换器的设计过程。在计算增益时,同时考虑了变压器次级的漏磁电感。

|